AI(Gemini)に次のような質問を投げかけて得られた回答を元に、ShrikeLiteで5分周回路を試してみました。質問「ステートマシンを利用してシステムクロックを5分周する回路をverilogで記述してください」

Geminiの回答をForgeFPGAworkshopのmain.vの下の方に別のmoduleとしてコピペし、topモジュール内で次のように記述しました。Verilogの文法は勉強中ですが、AIに教えてもらいながら何とかやりたいことはできました。

//divider to generate 10MHz

clock_divider_5 divid5(

.clk(clk),

.reset_n(rst_n),

.clk_out(clk10MHz)

);

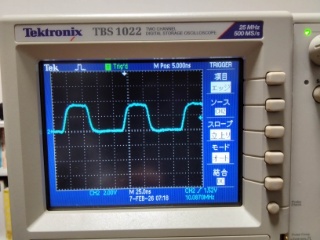

reg clk10MHz;

assign debug1 = clk10MHz;Geminiの回答では、デューティー比が1:5になるので、次のように変更して2:5にしました。冒頭の画像は、その出力波形です。デジタルオシロの表示では周波数は10.09MHz前後でした。

case (state)

S0: begin

state <= S1;

clk_out <= 1'b1; // S0のタイミングでHighを出力

end

S1: begin

state <= S2;

clk_out <= 1'b1; // same as S1

end

S2: begin

state <= S3;

clk_out <= 1'b0;

end

S3: begin

state <= S4;

clk_out <= 1'b0;

end

S4: begin

state <= S0;

clk_out <= 1'b0;

end

default: begin

state <= S0;

clk_out <= 1'b0;

end

endcase

コメント